#### **PAPER • OPEN ACCESS**

## A Linear 0.98 mV Low-Dropout Voltage Regulator in 0.18-µm CMOS Technology

To cite this article: S.A.Z. Murad et al 2021 J. Phys.: Conf. Ser. 1755 012049

View the article online for updates and enhancements.

#### You may also like

- Low quiescent current LDO with FVFbased PSRR enhanced circuit for EEG recording wearable devices

Kenji Mii, Daisuke Kanemoto and Tetsuya Hirose

- <u>Ultra-low power low-dropout linear</u> regulator with a load current tracking bias current generator for loT devices Yosuke Mizuno, Hikaru Sebe, Daisuke Kanemoto et al.

- <u>A fully on-chip fast-transient NMOS low</u> dropout voltage regulator with quasi floating gate pass element Han Wang, Chao Gou and Kai Luo

# Join the Society Led by Scientists, for Scientists Like You!

This content was downloaded from IP address 49.50.236.216 on 28/05/2025 at 04:02

Journal of Physics: Conference Series

### A Linear 0.98 mV Low-Dropout Voltage Regulator in 0.18-μm CMOS Technology

S.A.Z Murad<sup>1</sup>, A. Harun<sup>1</sup>, M.N.M. Isa<sup>1</sup>, A. Marzuki<sup>2</sup> and R. Sapawi<sup>3</sup>

<sup>1</sup>School of Microelectronic Engineering, Campus Alam UniMAP, Pauh Putra, 02600 Arau, Perlis, Malaysia

<sup>2</sup>School of Electrical and Electronic Engineering, Universiti Sains Malaysia,

Engineering Campus, 14300 Nibong Tebal, Pulau Pinang, Malaysia

<sup>3</sup>Faculty of Engineering, Universiti Malaysia Sarawak, 94399 Kota Samarahan, Sarawak, Malaysia

E-mail: sohiful@unimap.edu.my

**Abstract**. This paper presents a linear low-dropout (LDO) voltage regulator in 0.18-µm CMOS technology. The proposed LDO consists of voltage reference, error amplifier, pass device, output capacitor and resistive feedback network. A symmetrical operational transconductance amplifier (OTA) is implemented as an error amplifier and a PMOS transistor is used as a pass device to produce low dropout voltage and low quiescent current. The proposed design is simulated using Spectre simulator in Cadence software to verify its performances. The simulation results indicated that the LDO regulator achieves a regulated output voltage of 1.5 V with the ranges of supply voltage from 1.7 V to 2.0 V. The LDO regulator has a dropout voltage of 19.3 mV under maximum load current of 1.1 mA. The proposed LDO regulator is suitable for power management system.

#### 1. Introduction

Due to rising demand on the portable electronics devices, an on-chip power management system is required to stable the output voltage and prolonged battery life [1]. The power management system contains several components including linear voltage regulator, switching regulator and control logic. In general, a large voltage drop between the input and the output is required to ensure the linear voltage regulators function correctly [2]. A linear low dropout (LDO) voltage regulator is one of the linear voltage regulator circuit that can maintain the constant output voltages for any variation in the supply voltage or load currents. The LDO linear regulators are used to perform two functions; the first function is varying or regulates the output voltage required by the load. The second function is to keep the output voltage constant at the require value in spite of variation in the load current or supply voltage [3][4]. In fact, these functions are their main advantageous over the switching converters, where noise isolation and emissions are major system concerns.

The essential fundamental building block of power management unit is LDO regulator which is used in many portable batteries powered systems [5][6]. Since the constant and stable output voltage of LDO regulator independent of the load impedance, input voltage variation, temperature and time is required as the battery discharges. This characteristic leads to crucial stability improvement and noise reduction

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI. Published under licence by IOP Publishing Ltd 1

| 5th International Conference on Electronic Des | IOP Publishing     |                                     |  |

|------------------------------------------------|--------------------|-------------------------------------|--|

| Journal of Physics: Conference Series          | 1755 (2021) 012049 | doi:10.1088/1742-6596/1755/1/012049 |  |

for subsequent circuits. Due to the rapid growth of technology trend, designers are forced to design circuits operating at lower supply voltages. Thus, the LDO regulators are developed as they are ideal for giving multiple voltage levels and operate with a rather low dropout voltage. In addition, the LDO regulators also have capability of minimizing current consumption down to microamperes, which is important for current consumption of the sub-block in sleep mode. Another important characteristic of linear voltage regulator is their ability to suppress supply voltage noise, thus shielding the noise-sensitive blocks. Thus, PSRR is an important parameter of linear regulators. Besides that, the LDO linear voltage regulators are mostly used in IC design due to their performance, low cost and simplicity [5]. Therefore, the demand for the LDO regulators is increasing due to the higher demand of portable gadgets such as mobile phones, laptops, pagers as well as industrial and automotive applications [7].

Many types of LDO regulators have been proposed in the previous works to enhance the performance of the LDO regulators [1][2][5][13][17]. The most important parameters in designing the LDO regulator are the dropout voltage. Thus, the LDO voltage regulator has been designed by using bulk modulation technique that modulates the bulk voltage of the pass element to improve the dropout voltage of the LDO regulator [12]. The proposed LDO regulator has the dropout voltage of 200 mV. Besides that, the LDO voltage linear regulator based on a two-stage cascoded OTA as error amplifier is proposed in 0.13-µm CMOS technology has lower dropout voltage of 32 mV [16]. Based on the previously published works, the low dropout voltage can be achieved from 30 mV to 200 mV.

In this paper, a novel LDO voltage regulator is proposed using 0.18-µm CMOS technology. A symmetrical OTA as an error amplifier with a PMOS transistor as a pass element are employed to reduce the dropout voltage.

#### 2. Circuit Design

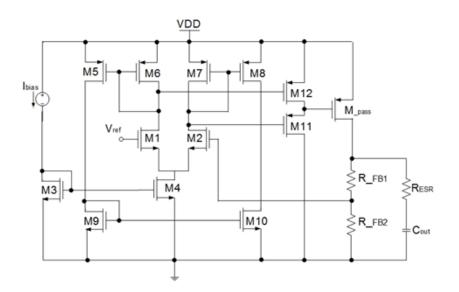

The schematic design of the proposed low-dropout (LDO) voltage regulator is presented in **Figure 1**. All bulks of NMOS transistors are connected to ground and all bulks of PMOS are connected to supply. The circuit consists of a symmetrical operational transconductance amplifier (OTA), a voltage reference, a PMOS pass transistor, an external load capacitor with small value of equivalent series resistance (ESR), and a resistive feedback network. The voltage reference is used to bias the differential pair of M1 and M2 and the biasing transistor of M4 to stay in saturation region. Symmetrical OTA as an error amplifier in negative feedback condition detects an error signal when there is a difference between the feedback voltage and reference voltage. Transistors M3, M4, M5, M6, M7, M8, M9 and M10 form the simple current mirrors. Transistor  $M_{Pass}$  as a pass device is used to drain current from the supply to the load. Output capacitor Cout and equivalent series resistance RESR are connected in the output node to provide stability for the circuit. Resistive feedback network consists of resistors  $R_{FB1}$  and  $R_{FB2}$  operating as a voltage divider to set the voltage for M2.

The proposed LDO regulator is designed based on the following parameters. The input voltage range is 1.7 V to 2.0 V, an input reference voltage is 1.2 V, an output voltage is 1.5 V and a biasing current is 100 nA.

Journal of Physics: Conference Series

**IOP** Publishing

Figure 1. The proposed LDO voltage regulator schematic.

#### 3. Simulation Results

Three types of analysis are performed to verify the LDO regulator performance includes DC analysis, transient analysis and AC analysis. The DC analysis focuses on steady state parameters of the LDO. Meanwhile, transient analysis computes the LDO's response as a function of time and AC analysis calculates the small-signal response of the LDO regulator.

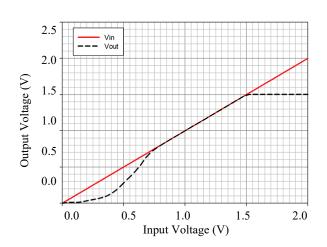

The input-output voltage characteristics of the proposed LDO regulator is obtained by sweeping the DC input voltage supply from 0 V to 2 V as shown in **Figure 2**. The characteristic is obtained under maximum load current ( $I_{load}$ ) conditions of 1.1 mA in order to verify the dropout voltage value. As observed from **Figure 2**, the output voltage of 1.5 V remains regulated for an input voltage range from 1.5 V to 2 V. The dropout voltage value was obtained at the beginning of the regulation region of VDO = 19.3 mV@V<sub>out</sub> = 1.5 V. There is no dropout voltage in the dropout region since the input voltage increases linearly with the output voltage. According to the result, it can be seen that the LDO regulator is in the regulation region when the output voltage level is high enough so that the LDO regulator can perform its two main functions such as keep the output voltage stable and deliver the required current to the load.

The line regulation is defined as the change at the output voltage in response to a change in the input voltage at a constant load current as express in equation (1).

$$Line \ regulation = \frac{\Delta V_{out}}{\Delta V_{in}} \tag{1}$$

5th International Conference on Electronic Design (ICED) 2020

Journal of Physics: Conference Series

**1755** (2021) 012049 doi:10.1088/1742-6596/1755/1/012049

**IOP** Publishing

Figure 2. Input-output characteristics when the output voltage is  $V_{out} = 1.5V$ .

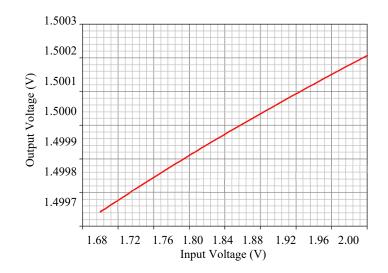

**Figure 3** illustrates how the output voltage changes with the input voltage when the LDO operates in the linear region (regulating region). As can be seen, the line regulation of 1.67 mV/V is obtained for an output voltage of 1.5 V at a constant load current of 1.1 mA.

**Figure 3.** LDO regulator line regulation at  $V_{out} = 1.5V$ .

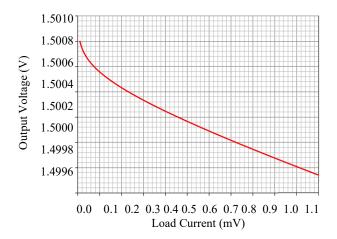

**Figure 4** shows the load regulation when Vin is 1.7 V under maximum load current ( $I_{load}$ ) conditions of 1.1 mA. The definition of load regulation is the change at the output voltage due to a change at the load current keeping the input voltage constant as given in equation (2).

$$Load \ regulation = \frac{\Delta V_{out}}{\Delta I_{out}}$$

(2)

Solving equation (2) with the values from the **Figure 4** results in a load regulation of 0.92 mV/mA for the output voltage of 1.5 V when the load current changes from 10  $\mu$ A to 1.1 mA.

Journal of Physics: Conference Series

1755 (2021) 012049

2049 doi:10.1088/1742-6596/1755/1/012049

**Figure 4.** LDO regulator load regulation at  $V_{out} = 1.5V$ .

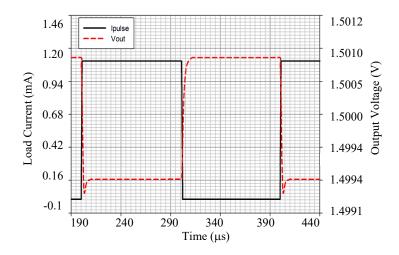

The other important parameters of LDO regulator are line and load transient responses. **Figure 5** shows the load transient response with frequency of 5 kHz. As observed, there is a small overshoot in the LDO output voltage which is in the range of millivolts. The overshoot is mainly caused by the equivalent series resistance (ESR) of the output capacitor. The larger of the current step and ESR, the larger the overshoot due to the capacitor is trying to source the current to the load.

Figure 5. Load transient from 10 µA to 1.1 mA at 5 kHz.

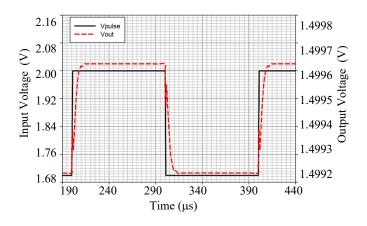

**Figure 6** depicts the line transient response for maximum load current 1.1 mA. As can be seen, it is clearly when the voltage rises, the response is fast, because the capacitor is charged by the current from the supply, but when the voltage drops, the output capacitor holds its value for quite a long time. This is because it is discharged only by a small amount of load current.

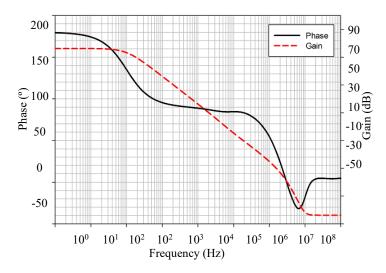

The LDO's stability parameter is measure by phase and gain margin. The phase margin needs to be at least 45° in order to has a stable system. **Figure 7** shows the bode plot of open loop gain and phase

| 5th International Conference on Electronic Design (ICED) 2020 |                    | IOP Publishing                      |  |  |

|---------------------------------------------------------------|--------------------|-------------------------------------|--|--|

| Journal of Physics: Conference Series                         | 1755 (2021) 012049 | doi:10.1088/1742-6596/1755/1/012049 |  |  |

over. The gain margin (GM) and the phase margin (PM) are plotted over frequency range from 1 Hz to 100 MHz. The GM is obtained when the phase is equal to 0°. The GM of the LDO regulator is -19.34 dB. Similarly, the PM margin is attained when the open-loop gain is equal to 0 dB. The LDO regulator has the phase margin of 69.5°. Therefore, the system is in stable condition.

Figure 6. Line transient from 1.7 V to 2 V for load current of 1.1 mA.

Figure 7. Bode plot of the proposed LOD.

The proposed LDO regulator is compared with other related works as shown in **Table I**. The LDO regulator with a double recycling folded cascode as an error amplifier is proposed in [13] and [17] produces the dropout voltage of 200 mV. The proposed LDO regulator in [16] which implements a main error amplifier and a bulk error amplifier with the bulk modulation technique provides the dropout voltage of 200 mV. The proposed LDO voltage regulator based on a two-stage cascoded OTA as an error amplifier with body driven technique in [16] gives same dropout voltage of 200 mV. In [14], the proposed LDO achieves low dropout voltage of 32 mV with a constant input voltage at 5 V. The proposed LDO in this work which implements a symmetrical OTA gives the lowest dropout voltage of 19.3 mV as compared to the others LDO regulators. In addition, the LDO achieves better line regulation as compared to the others LDO regulators. Moreover, the proposed LDO obtains the line regulation of 1.67 mV/V makes it as a useful choice in battery-powered portable applications, where the input voltage

| 5th International Conference on Electronic Desi | IOP Publishing     |                                     |  |

|-------------------------------------------------|--------------------|-------------------------------------|--|

| Journal of Physics: Conference Series           | 1755 (2021) 012049 | doi:10.1088/1742-6596/1755/1/012049 |  |

is changing due to the battery discharging. Besides that, the proposed design has higher power supply rejection (PSR) of -54.92 dB when compared to the proposed LDO regulator in [12]. Based on Table I, the proposed LDO voltage regulator in this work indicate that the LDO is very promising to be implemented in power management for system on chip (SoC) applications.

#### 4. Conclusion

A linear low-dropout (LDO) voltage regulator in 0.18-µm CMOS technology is successfully designed and simulated. A low dropout voltage and low quiescent current is achieved by using a symmetrical operational transconductance amplifier (OTA) and a PMOS transistor as an error amplifier and a pass device, respectively. The simulation results indicated that the LDO regulator achieves a regulated output voltage of 1.5 V with the ranges of supply voltage from 1.7 V to 2.0 V. The LDO regulator has a dropout voltage of 19.3 mV under maximum load current of 1.1 mA. The proposed LDO regulator is suitable for power management system.

| Reference                 | [12]   | [13]  | [14]  | [15]   | [16]    | [17]    | [18]    | This<br>work |

|---------------------------|--------|-------|-------|--------|---------|---------|---------|--------------|

| Year                      | 2015   | 2017  | 2018  | 2018   | 2018    | 2019    | 2019    | 2020         |

| CMOS                      |        |       |       |        |         |         |         |              |

| Technology                | 0.18   | 0.13  | 0.13  | 0.18   | 0.18    | 0.18    | 0.18    | 0.18         |

| (µm)                      |        |       |       |        |         |         |         |              |

| Supply voltage            | 1.45-  | 1.2   | 5     | 1.8    | 2.0-3.3 | 1.2-1.8 | 1.8-2.6 | 1.7-2.0      |

| (V)                       | 2.0    | 1.2   | 0     | 110    | 2.0 5.5 | 1.2 1.0 | 1.0 2.0 | 1., 2.0      |

| Output voltage            | 1.4    | 1     | 4.5   | 0.5    | 1.8     | 1.2-1.8 | 1.6     | 1.5          |

| (V)                       |        |       |       |        |         |         |         |              |

| Dropout voltage           | 200    | 200   | 32.1  | 200    | 200     | 200     | 200     | 19.3         |

| (mV)                      |        |       |       |        |         |         |         |              |

| Load current $(m A)$      | 0-100  | 5     | 0.265 | 50     | -       | 100     | 50      | 1.1          |

| (mA)<br>Line regulation   |        |       |       |        |         |         |         |              |

| Line regulation<br>(mA/V) | 7.27   | -     | -     | 71.25  | 15.38   | -       | 15.7    | 1.67         |

| Load regulation           |        |       |       |        |         |         |         |              |

| (mV/mA)                   | 0.016  | 0.015 | -     | -0.438 | 0.8     | -       | -       | 0.92         |

| PSR at 1 kHz              |        |       |       |        |         |         |         |              |

| (dB)                      | -49.26 | -     | -     | -      | -       | -       | -       | -54.92       |

Table 1. Comparison with previously published LDO voltage regulators.

#### References

- [1] Murad, S. A. Z., Harun, A., Isa, M. N. M., Mohyar, S. N., Sapawi, R., & Karim, J., "Design of CMOS low-dropout voltage regulator for power management integrated circuit in 0.18-μm technology," 2nd Int. Con. On Appl. Phot. And Elect., 2019.

- [2] Al-Shyoukh M., Lee H., and Perez R., "A transient-enhanced low-quiescent current low-dropout regulator with buffer impedance attenuation," *IEEE J. Solid-State Circuits*, vol. 42, no. 8, 2007, pp. 1732–1741.

- [3] Murad, S.A.Z., Harun, A., Ramli, M.M., Isa, M.N.M., Sapawi, R., "High-speed low power CMOS comparator using forward body bias technique in 0.13 µm technology," J. of Telecom., Electr. and Comp. Engin., Vol. 10, no. 3, 2018, pp. 25-29.

**IOP** Publishing

Journal of Physics: Conference Series

- [4] Halim, W. W., Julie R. R, Suhaidi S., Yuzman Y. and Chia C. Y. "Study on Performance of Capacitor-less LDO with Different Types of Resistor." *IEEE Int. Circuits and Sys. Symposium* (ICSyS), 2019, pp. 1-5.

- [5] Mishra A.K. and Pandey R., "Design of CMOS low drop-out regulators : a comparative study," *Int. J. Comput. Technol.*, vol. 4, no. 2, 2013.

- [6] Anusha, G., Atul Kumar, and Kavindra Kandpal. "A Fully On-Chip Low-Dropout Regulator for SoC applications." *Procedia Comp. Sci. 171*, 2020, pp. 1009-1017.

- [7] Giustolisi G., PalumbG. o, and Spitale E., "Robust miller compensation with current amplifiers applied to LDO voltage regulators," *IEEE Trans. Circuits Syst. I Regul. Pap.*, vol. 59, no. 9, 2012, pp. 1880–1893.

- [8] Mart H., "Cascoded OTA based low dropout (LDO) voltage regulator," *Proc. 2014 IEEE Emerg. Technol. Fact. Autom.*, Barcelona, Spain, 2014, pp. 2–6.

- [9] Abiri E., Salehi M. R., and Mohammadalinejadi S., "A low dropout voltage regulator with enhanced transconductance error amplifier and small output voltage variations," *21<sup>st</sup> Iran. Conf. Electr. Eng. ICEE*, 2013, pp. 3–7.

- [10] Dwibedy D., Alapati S., Patri S., and Ksr K., "Fully on chip low dropout (LDO) voltage regulator with improved transient response," *IEEE Reg. 10 Annu. Int. Conf. Proc. TENCON*, 2015.

- [11] Mustafa N., Florence C., Mamun I. R., Waniiwan N., Noorfazila K., and Abdul M., "Design of a low drop-out voltage regulator using 0.13 µm CMOS technology." J. of Eng. Sci. and Tech., vol. 13, no. 5, 2018, pp. 1282-1298.

- [12] S Patri. R., Alapati,S. Chowdary S., and Prasad K., "250 mA ultra-low drop out regulator with high slew rate double recycling folded cascode error amplifier," 18<sup>th</sup> Int. Symp. VLSI Des. Test, VDAT, 2014, pp. 2–6.

- [13] Basra, P., and Sharma, A. K., "Design of low dropout (ldo) voltage regulator using bulk modulation," *Int. J. Electron. Commun. Eng. Technol.*, vol. 8, no. 3, 2017, pp. 59–66.

- [14] Xin C., Yu Z., Guangjun X., Yizhong Y., and Zhang Z., "An ultra-low power output capacitorless low-dropout regulator with slew-rate-enhanced circuit," *J. of Semicon.*, vol. 39, no. 3, 2018, pp. 1-5.

- [15] Bin M., Reaz I., and Irma W. et al., "Design of A Low Drop-Out Voltage Regulator Using 0.13μm CMOS Technology," J. Eng. Sci. Technol., vol. 13, no. 5, 2018, pp. 1282–1298.

- [16] Monika G., Sharma R.K., "Design of output capacitorless low dropout regulator with fast transition response," *IEEE 2<sup>nd</sup> Inter. Conf. on Intelligent Comp. and Control Syst.*, 2018, pp. 995-998.

- [17] J. Tang, J. Lee, J. Roh, and S. Member, "Low-Power Fast-Transient Capacitor-Less LDO Regulator with High Slew-Rate Class-AB Amplifier." *IEEE Trans. on Circuits and Syst. II: Express Briefs*, vol. 3, no. 66, 2019, pp. 462-466.

- [18] Zamora-M., Gregorio, Dario Edwin G., Huber G.N., Jaime M-C., Luis Armando M-C., José Miguel R-P, and Alejandro D. S., "A 0.18 μm CMOS capacitor-less Low-Drop Out Voltage Regulator Compensated via the Bootstrap Flipped-Voltage Follower." *Microelectronics J.*, vol. 101, 2020.